7–1 Latches

The S-R (SET-RESET) Latch

The Gated S-R Latch

The Gated D Latch

7-2 Flip-Flops

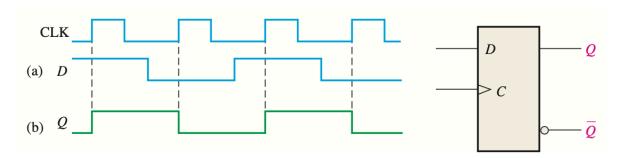

The D Flip-Flop

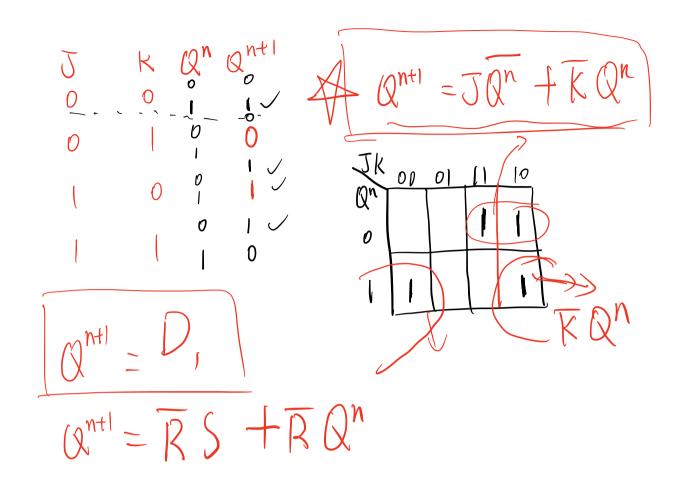

The J-K Flip-Flop

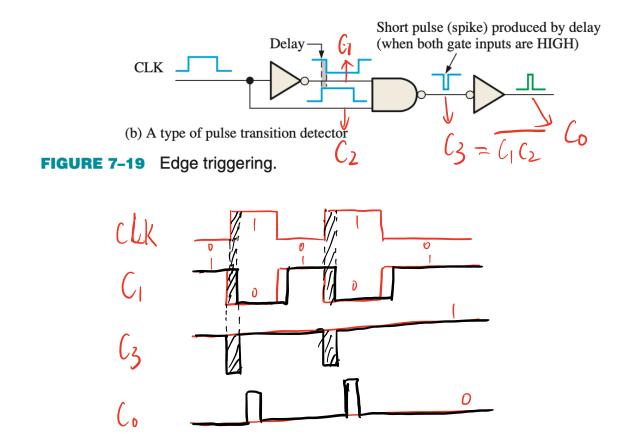

Edge-Triggered Operation-D Flip-Flop

J-K Flip-Flop

Asynchronous Preset and Clear Inputs

7-3 Flip-Flop Operating Characteristics

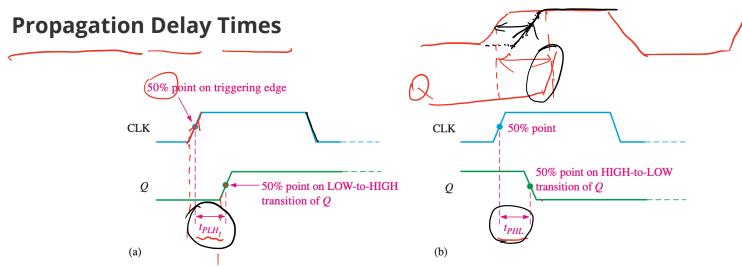

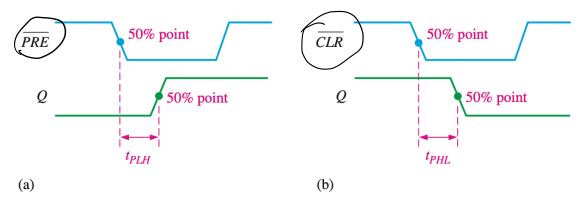

**Propagation Delay Times**

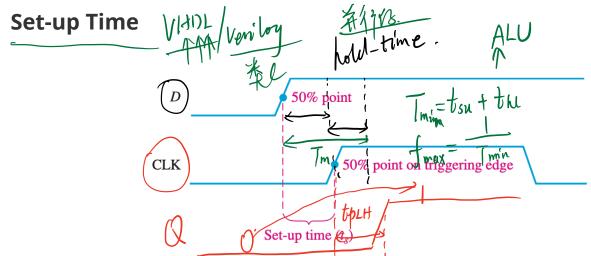

Set-up Time

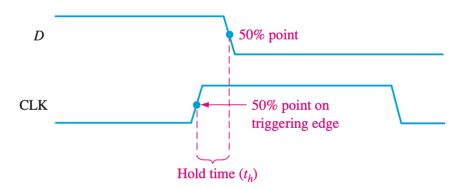

**Hold Time**

**Maximum Clock Frequency**

**Pulse Widths**

**Power Dissipation**

Comparison of Specific Flip-Flops

7-4 Flip-Flop Applications

Parallel Data Storage

**Frequency Division**

Counting

7-5 One-Shots

Nonretriggerable One-Shot

The 555 Timer as a One-Shot

7–6 The Astable Multivibrator

The 555 Timer as an Astable Multivibrator

# 7-1 Latches

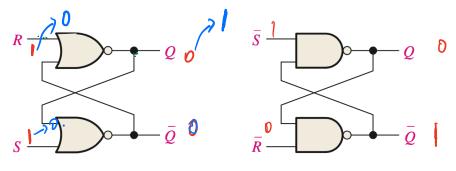

# The S-R (SET-RESET) Latch

$$\begin{array}{cccc}

v_i & & & & & \\

\hline

v_i & & \\

\hline

v_i & & \\

\hline

v_i & & \\

\hline

v_i & &$$

$$V_{i} = \frac{1}{V_{i} - V_{c}} = \frac{1}{C} V_{c}$$

$$V_{i} = \frac{1}{V_{i} - V_{c}} = \frac{1}{C} V_{c}$$

$$V_{i} =$$

(a) Active-HIGH input S-R latch

(b) Active-LOW input  $\bar{S}$ - $\bar{R}$  latch

**FIGURE 7–1** Two versions of SET-RESET (S-R) latches. Open files F07-01(a) and (b) and verify the operation of both latches. *A Multisim tutorial is available on the website.*

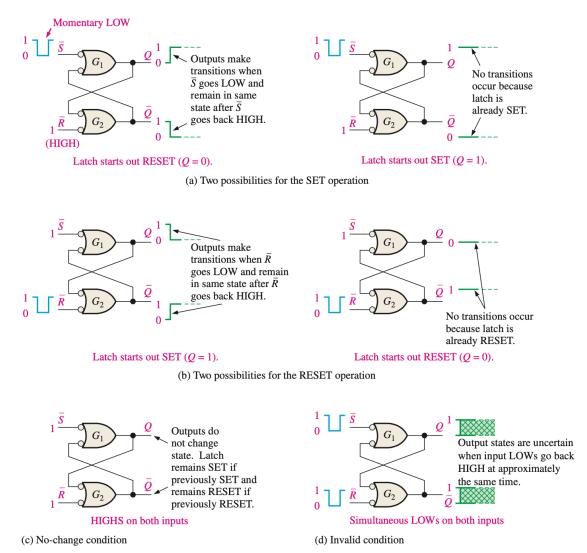

**FIGURE 7-3** The three modes of basic  $\overline{S}$ - $\overline{R}$  latch operation (SET, RESET, no-change) and the invalid condition.

## TABLE 7-1

Truth table for an active-LOW input  $\overline{S}-\overline{R}$  latch.

| Inputs Outputs |                | puts |                       |                                            |

|----------------|----------------|------|-----------------------|--------------------------------------------|

| $\overline{S}$ | $\overline{R}$ | Q    | $\overline{m{arrho}}$ | Comments                                   |

| 1              | 1              | NC   | NC                    | No change. Latch remains in present state. |

| 0              | 1              | 1    | 0                     | Latch SET.                                 |

| 1              | 0              | 0    | 1                     | Latch RESET.                               |

| 0              | 0              | 1    | 1                     | Invalid condition                          |

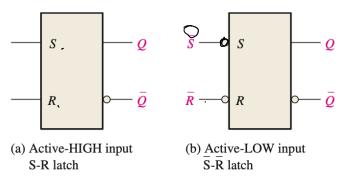

Logic symbols for both the active-HIGH input and the active-LOW input latches are shown in Figure 7–4.

**FIGURE 7–4** Logic symbols for the S-R and  $\overline{S}-\overline{R}$  latch.

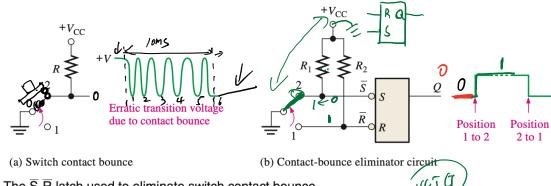

## An Application

#### The Latch as a Contact-Bounce Eliminator

A good example of an application of an  $\overline{S}$ - $\overline{R}$  latch is in the elimination of mechanical switch contact "bounce." When the pole of a switch strikes the contact upon switch closure, it physically vibrates or bounces several times before finally making a solid contact. Although these bounces are very short in duration, they produce voltage spikes that are often not acceptable in a digital system. This situation is illustrated in Figure 7–6(a).

**FIGURE 7–6** The  $\overline{S}-\overline{R}$  latch used to eliminate switch contact bounce.

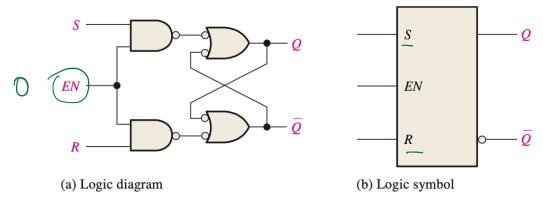

# The Gated S-R Latch

FIGURE 7–8 A gated S-R latch.

# Determine the *Q* output waveform if the inputs shown in Figure 7–9(a) are applied to a gated S-R latch that is initially RESET. S R O (a) (b) Q D FIGURE 7–9

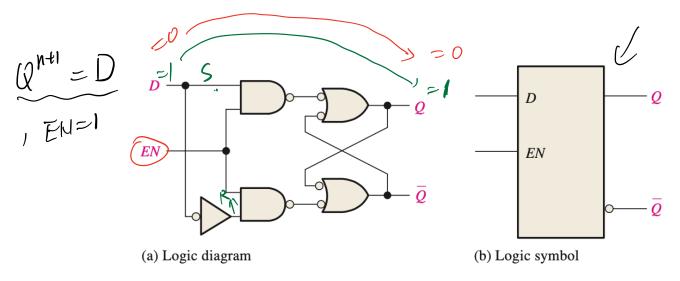

# The Gated D Latch

FIGURE 7-10 A gated D latch. Open file F07-10 and verify the operation.

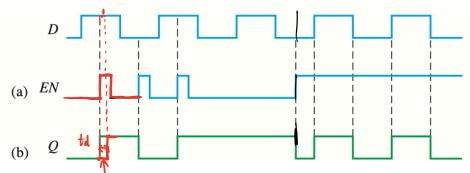

Determine the Q output waveform if the inputs shown in Figure 7–11(a) are applied to a gated D latch, which is initially RESET.

FIGURE 7-11

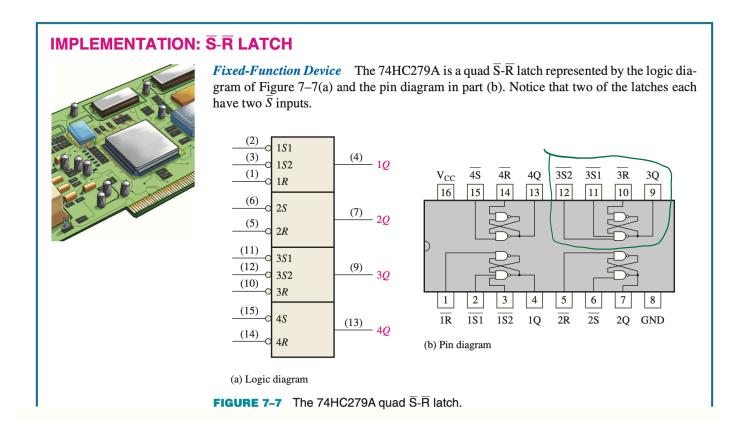

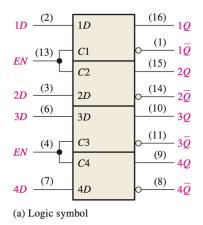

## **IMPLEMENTATION: GATED D LATCH**

**Fixed-Function Device** An example of a gated D latch is the 74HC75 represented by the logic symbol in Figure 7–12(a). The device has four latches. Notice that each active-HIGH EN input is shared by two latches and is designated as a control input (C). The truth table for each latch is shown in Figure 7–12(b). The X in the truth table represents a "don't care" condition. In this case, when the EN input is LOW, it does not matter what the D input is because the outputs are unaffected and remain in their prior states.

| Inputs                                            | Outputs            |           |  |  |  |

|---------------------------------------------------|--------------------|-----------|--|--|--|

| $\underline{\underline{D}}$ $\underline{EN}$      | $Q^{nt}$ $\bar{Q}$ | Comments  |  |  |  |

| 0 1                                               | 0 1                | RESET 🖊   |  |  |  |

| 1 1                                               | 1 0                | SET ⇐     |  |  |  |

| $\begin{pmatrix} X \end{pmatrix} = 0$             | $Q_0$ $ar{Q}_0$    | No change |  |  |  |

|                                                   | 7                  |           |  |  |  |

| Notes O is the series and the least the indicated |                    |           |  |  |  |

Note:  $Q_0$  is the prior output level before the indicated input conditions were examined.

(b) Truth table (each latch)

FIGURE 7-12 The 74HC75 quad D latch.

# 7-2 Flip-Flops

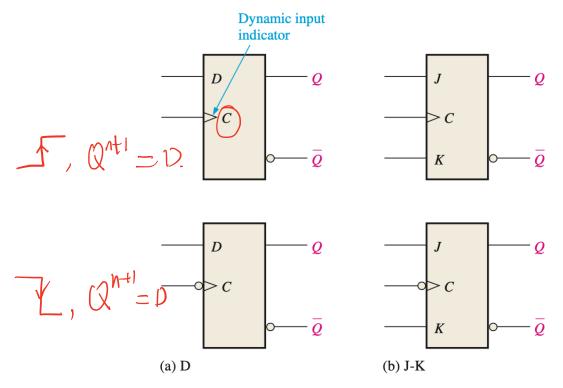

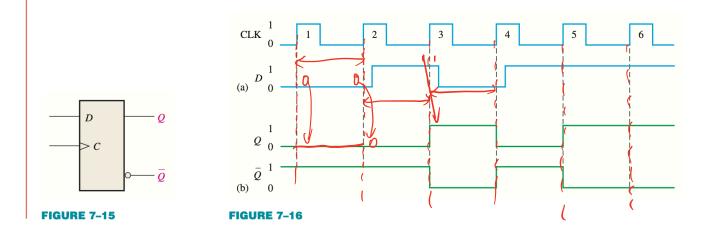

An edge-triggered flip-flop changes state either at the positive edge (rising edge) of at the negative edge (falling edge) of the clock pulse and is sensitive to its inputs only at this transition of the clock. Two types of edge-triggered flip-flops are covered in this section: D and J-K. The logic symbols for these flip-flops are shown in Figure 7–13. Notice that each type can be either positive edge-triggered (no bubble at C input) or negative edge-triggered (bubble at C input). The key to identifying an edge-triggered flip-flop by its logic symbol is the small triangle inside the block at the clock (C) input. This triangle is called the *dynamic input indicator*.

**FIGURE 7–13** Edge-triggered flip-flop logic symbols (top: positive edge-triggered; bottom: negative edge-triggered).

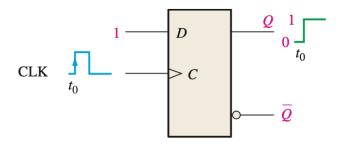

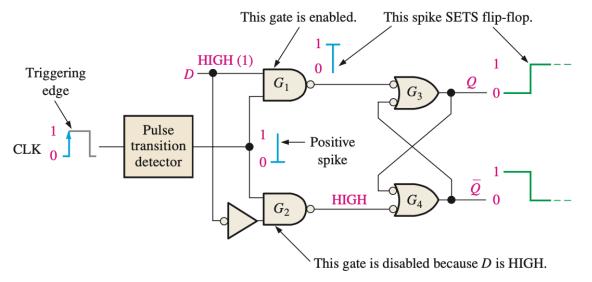

# The D Flip-Flop

- (a) D = 1 flip-flop SETS on positive clock edge. (If already SET, it remains SET.)

- (b) D = 0 flip-flop RESETS on positive clock edge. (If already RESET, it remains RESET.)

**FIGURE 7–14** Operation of a positive edge-triggered D flip-flop.

## **TABLE 7–2**

Truth table for a positive edge-triggered D flip-flop.

| Inputs   |                         | Ou |                               |          |

|----------|-------------------------|----|-------------------------------|----------|

| D        | CLK                     | Q  | $\overline{oldsymbol{arrho}}$ | Comments |

| <u> </u> | $\uparrow$              | 0  | 1                             | RESET    |

| 1        | $\left(\uparrow\right)$ | 1  | 0                             | SET      |

† = clock transition LOW to HIGH

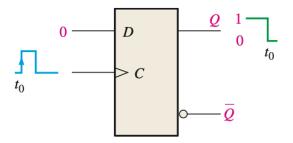

#### **EXAMPLE 7-4**

Determine the Q and  $\overline{Q}$  output waveforms of the flip-flop in Figure 7–15 for the D and CLK inputs in Figure 7–16(a). Assume that the positive edge-triggered flip-flop is initially RESET.

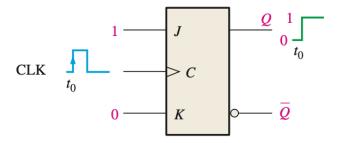

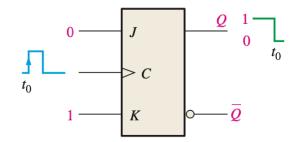

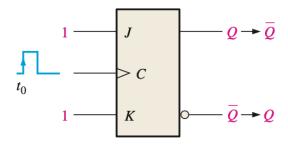

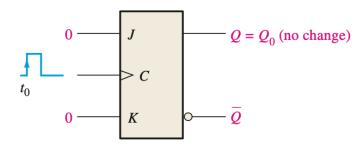

The J-K Flip-Flop

- (a) J = 1, K = 0 flip-flop SETS on positive clock edge. (If already SET, it remains SET.)

- (b) J = 0, K = 1 flip-flop RESETS on positive clock edge. (If already RESET, it remains RESET.)

- (c) J = 1, K = 1 flip-flop changes state (toggle).

- (d) J = 0, K = 0 flip-flop does not change. (If SET, it remains SET; if RESET, it remains RESET.)

FIGURE 7-17 Operation of a positive edge-triggered J-K flip-flop.

## TABLE 7-3

Truth table for a positive edge-triggered J-K flip-flop.

| Inputs                                         |            |             | Outputs          |                         |                     |  |

|------------------------------------------------|------------|-------------|------------------|-------------------------|---------------------|--|

| Jump                                           | $K_{eep}$  | CLK         | Q                | $\overline{m{\varrho}}$ | Comments            |  |

| 0                                              | 0          | <u> </u>    | $Q_0$            | $\overline{Q}_0$        | No change <         |  |

| 0                                              | 14         | <u> </u>    | $Q_0$            | 1                       | RESET               |  |

| <del>&gt;</del> 1                              | 0          | <u></u>     | 1                | 0                       | SET <               |  |

| 1                                              | 1          | $(\hat{1})$ | $\overline{Q}_0$ | $ ightharpoonup Q_0$    | Toggle $\leftarrow$ |  |

| $\uparrow$ = clock tran                        | sition LOW | to HIGH     | <b>₩</b>         |                         |                     |  |

| $Q_0$ = output level prior to clock transition |            |             | Qn               | 41 =                    | Qn                  |  |

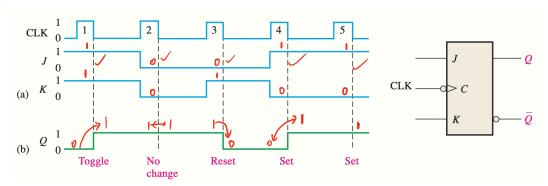

## **EXAMPLE 7-5**

The waveforms in Figure 7–18(a) are applied to the J, K, and clock inputs as indicated. Determine the Q output, assuming that the flip-flop is initially RESET.

FIGURE 7-18

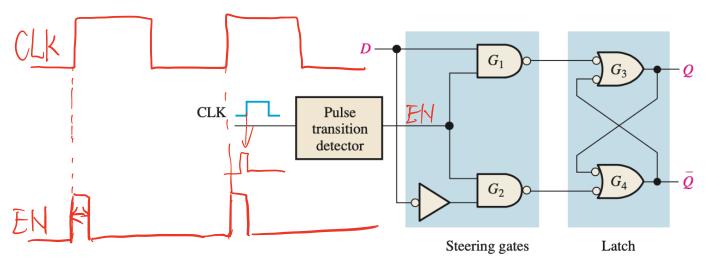

# **Edge-Triggered Operation-D Flip-Flop**

(a) A simplified logic diagram for a positive edge-triggered D flip-flop

**FIGURE 7–20** Flip-flop making a transition from the RESET state to the SET state on the positive-going edge of the clock pulse.

**FIGURE 7–21** Flip-flop making a transition from the SET state to the RESET state on the positive-going edge of the clock pulse.

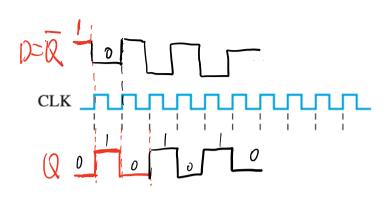

Given the waveforms in Figure 7–22(a) for the D input and the clock, determine the Q output waveform if the flip-flop starts out RESET.

**FIGURE 7–22**

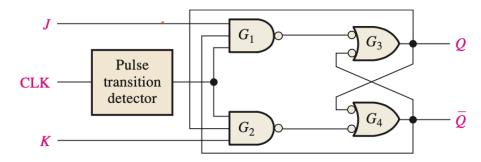

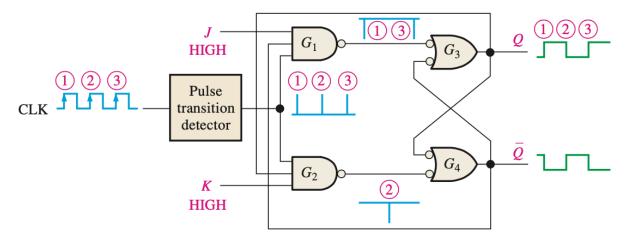

# J-K Flip-Flop

FIGURE 7-23 A simplified logic diagram for a positive edge-triggered J-K flip-flop.

FIGURE 7–24 Transitions illustrating flip-flop operation.

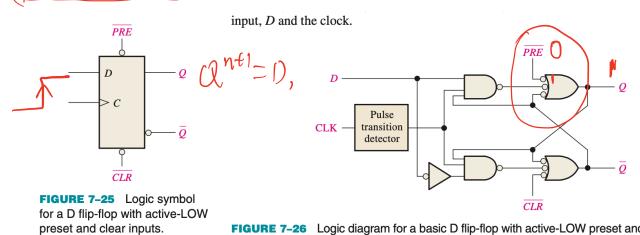

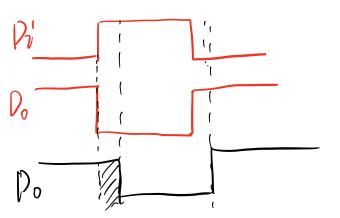

# **Asynchronous Preset and Clear Inputs**

FIGURE 7–26 Logic diagram for a basic D flip-flop with active-LOW preset and clear inputs.

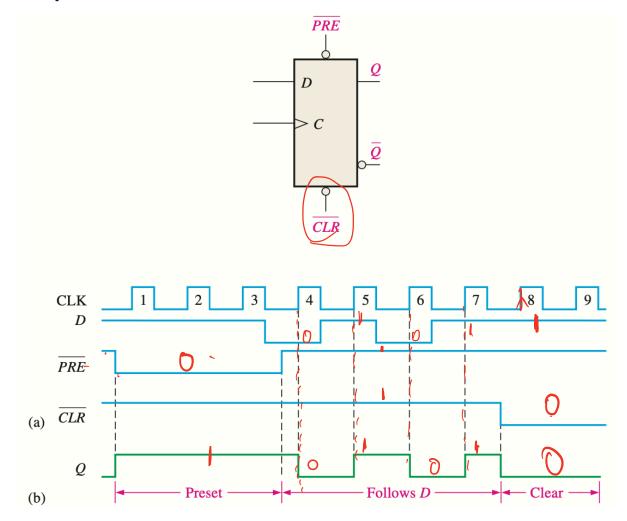

For the positive edge-triggered D flip-flop with preset and clear inputs in Figure 7–27, determine the Q output for the inputs shown in the timing diagram in part (a) if Q is initially LOW.

**FIGURE 7–27** Open file F07-27 to verify the operation.

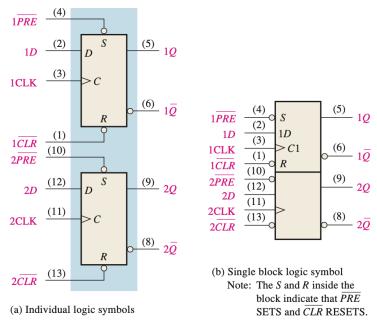

## **IMPLEMENTATION: D FLIP-FLOP**

**Fixed-Function Device** The 74HC74 dual D flip-flop contains two identical D flip-flops that are independent of each other except for sharing  $V_{\rm CC}$  and ground. The flip-flops are positive edge-triggered and have active-LOW asynchronous preset and clear inputs. The logic symbols for the individual flip-flops within the package are shown in Figure 7–28(a), and an ANSI/IEEE standard single block symbol that represents the entire device is shown in part (b). The pin numbers are shown in parentheses.

**FIGURE 7–28** The 74HC74 dual positive edge-triggered D flip-flop.

## **EXAMPLE 7–8**

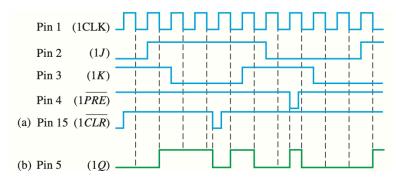

The 1J, 1K, 1CLK,  $1\overline{PRE}$ , and  $1\overline{CLR}$  waveforms in Figure 7–30(a) are applied to one of the negative edge-triggered flip-flops in a 74HC112 package. Determine the 1Q output waveform.

Latches, Flip-Flops, and Timers

FIGURE 7-30

# 7-3 Flip-Flop Operating Characteristics

FIGURE 7-31 Propagation delays, clock to output.

FIGURE 7-32 Propagation delays, preset input to output and clear input to output.

**FIGURE 7–33** Set-up time  $(t_s)$ . The logic level must be present on the D input for a time equal to or greater than  $t_s$  before the triggering edge of the clock pulse for reliable data entry.

## **Hold Time**

**FIGURE 7–34** Hold time  $(t_h)$ . The logic level must remain on the D input for a time equal to or greater than  $t_h$  after the triggering edge of the clock pulse for reliable data entry.

# **Maximum Clock Frequency**

## **Pulse Widths**

# **Power Dissipation**

$$P = V_{CC} * I_{CC}$$

# **Comparison of Specific Flip-Flops**

## TABLE 7-4

Comparison of operating parameters for four IC families of flip-flops of the same type at 25°C.

|                                               | CMOS     |         | Bipolar (TTL) |         |  |

|-----------------------------------------------|----------|---------|---------------|---------|--|

| Parameter                                     | 74HC74A  | 74AHC74 | 74LS74A       | 74F74   |  |

| $t_{PHL}$ (CLK to $Q$ )                       | 17 ns    | 4.6 ns  | 40 ns         | 6.8 ns  |  |

| $t_{PLH}$ (CLK to $Q$ )                       | 17 ns    | 4.6 ns  | 25 ns         | 8.0 ns  |  |

| $t_{PHL}(\overline{CLR} \text{ to } Q)$       | 18 ns    | 4.8 ns  | 40 ns         | 9.0 ns  |  |

| $t_{PLH}(\overrightarrow{PRE} \text{ to } Q)$ | 18 ns    | 4.8 ns  | 25 ns         | 6.1 ns  |  |

| $t_s$ (set-up time)                           | 14 ns    | 5.0 ns  | 20 ns         | 2.0  ns |  |

| $t_h$ (hold time)                             | 3.0 ns   | 0.5 ns  | 5 ns          | 1.0  ns |  |

| $t_W$ (CLK HIGH)                              | 10 ns    | 5.0 ns  | 25 ns         | 4.0 ns  |  |

| $t_W$ (CLK LOW)                               | 10 ns    | 5.0 ns  | 25 ns         | 5.0 ns  |  |

| $t_W(\overline{CLR}/\overline{PRE})$          | 10 ns    | 5.0 ns  | 25 ns         | 4.0 ns  |  |

| $f_{max}$                                     | 35 MHz   | 170 MHz | 25 MHz        | 100 MHz |  |

| Power, quiescent                              | 0.012 mW | 1.1 mW  |               |         |  |

| Power, 50% duty cycle                         |          |         | 44 mW         | 88 mW   |  |

7-4 Flip-Flop Applications

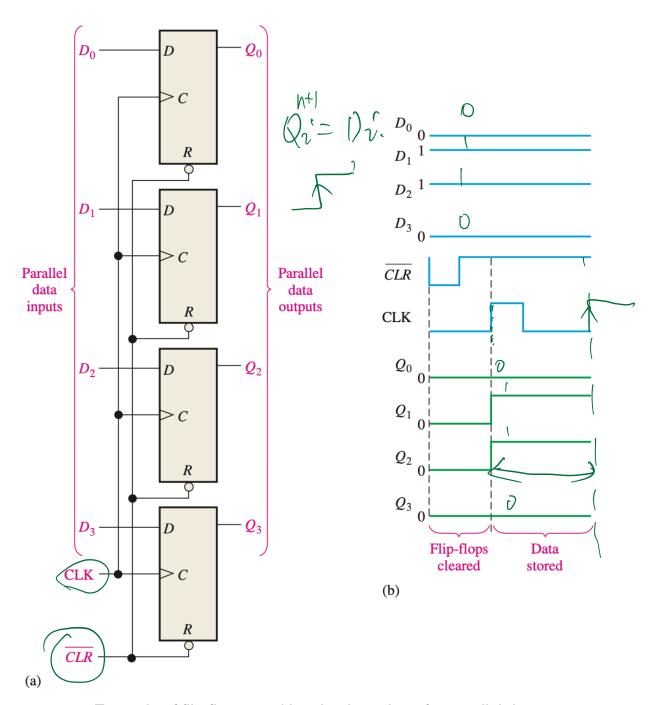

**Parallel Data Storage**

2+1=3h>

$\frac{1}{3}$   $\approx$  330 MH  $^2$

FIGURE 7-35 Example of flip-flops used in a basic register for parallel data storage.

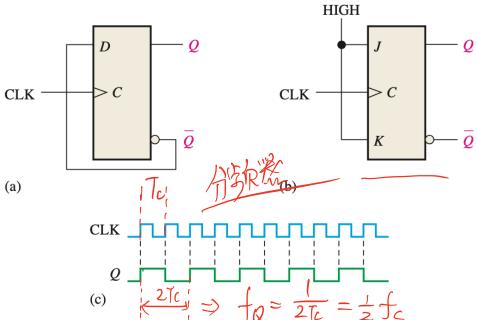

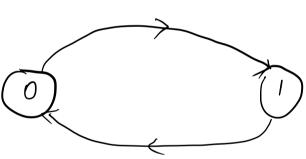

# **Frequency Division**

**FIGURE 7–36** The D flip-flop and J-K flip-flop as a divide-by-2 device. *Q* is one-half the frequency of CLK. Open file F07-36 and verify the operation.

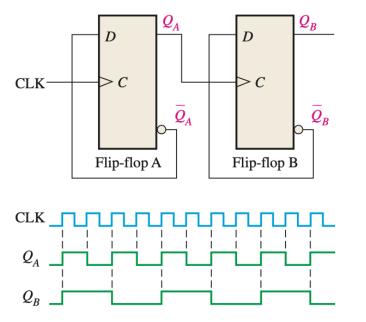

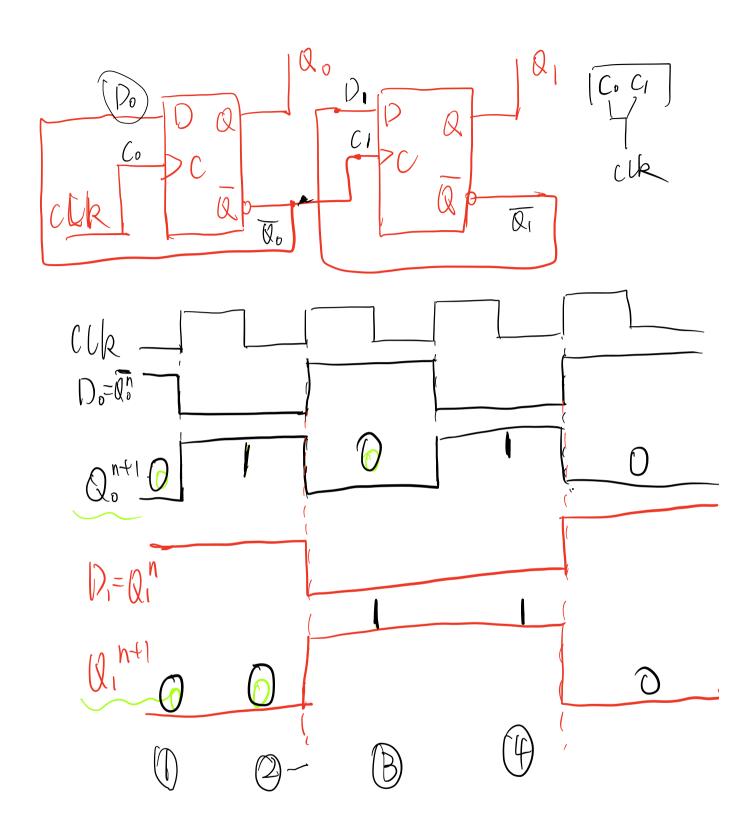

**FIGURE 7–37** Example of two D flip-flops used to divide the clock frequency by 4.  $Q_A$  is one-half and  $Q_B$  is one-fourth the frequency of CLK. Open file F07-37 and verify the operation.

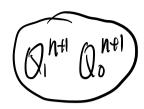

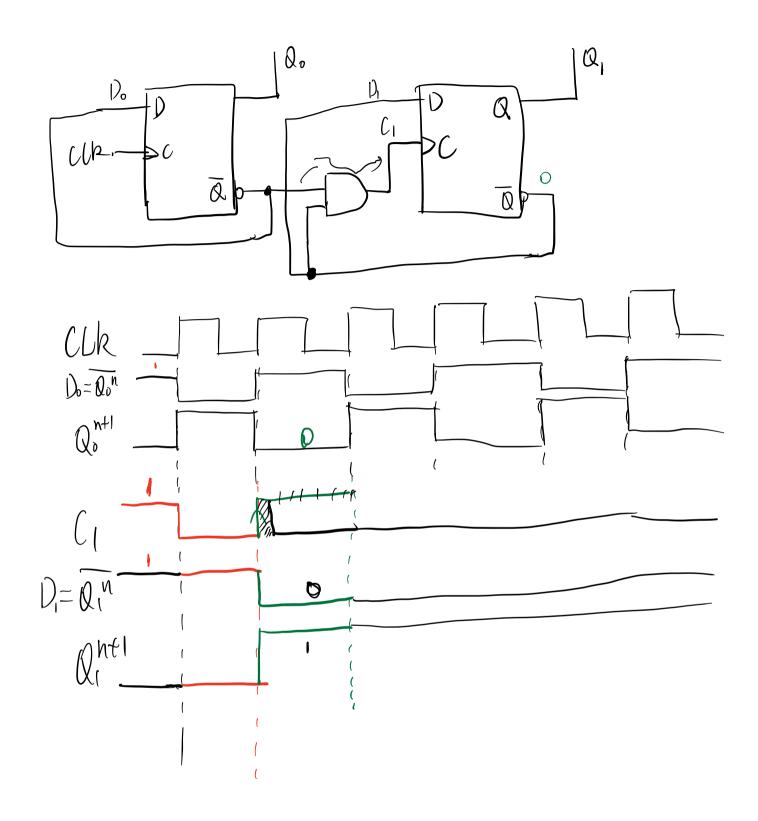

$$Q^{n+1} = D$$

,  $D = \overline{Q^n}$   $Y = Q^{n+1}$  数分程 , ③车辆数分程

$$D = \overline{\mathbb{Q}^n}$$

米发.图

$$CLK \qquad D=\overline{Q^n} \qquad Q^{n+1} = D \qquad Q^{n+1} = D$$

$$Q^{n+1} = D \qquad D=\overline{Q^n} \qquad D=\overline{Q$$

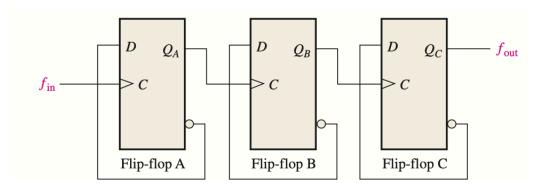

Develop the  $f_{\text{out}}$  waveform for the circuit in Figure 7–38 when an 8 kHz square wave input is applied to the clock input of flip-flop A.

FIGURE 7-38

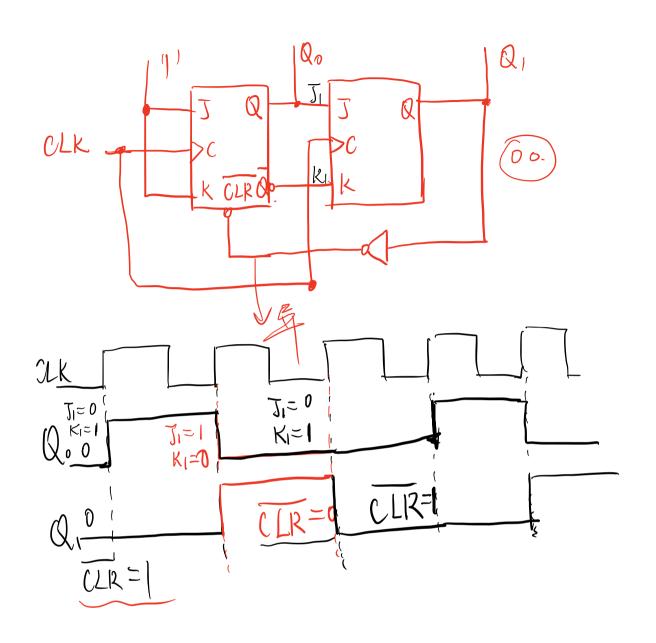

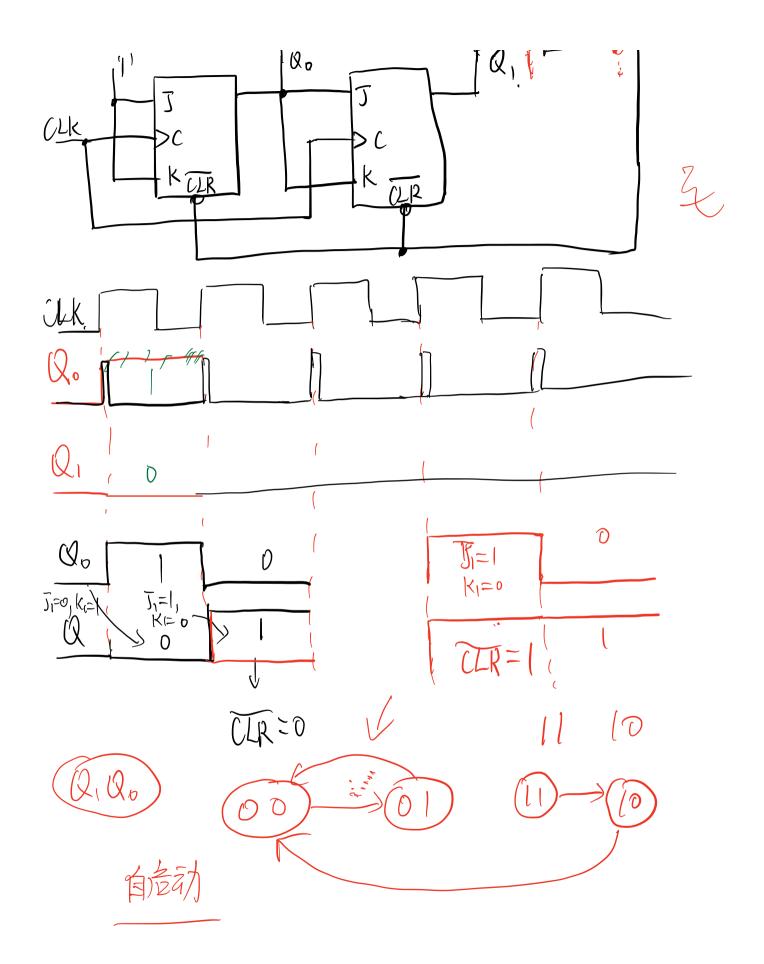

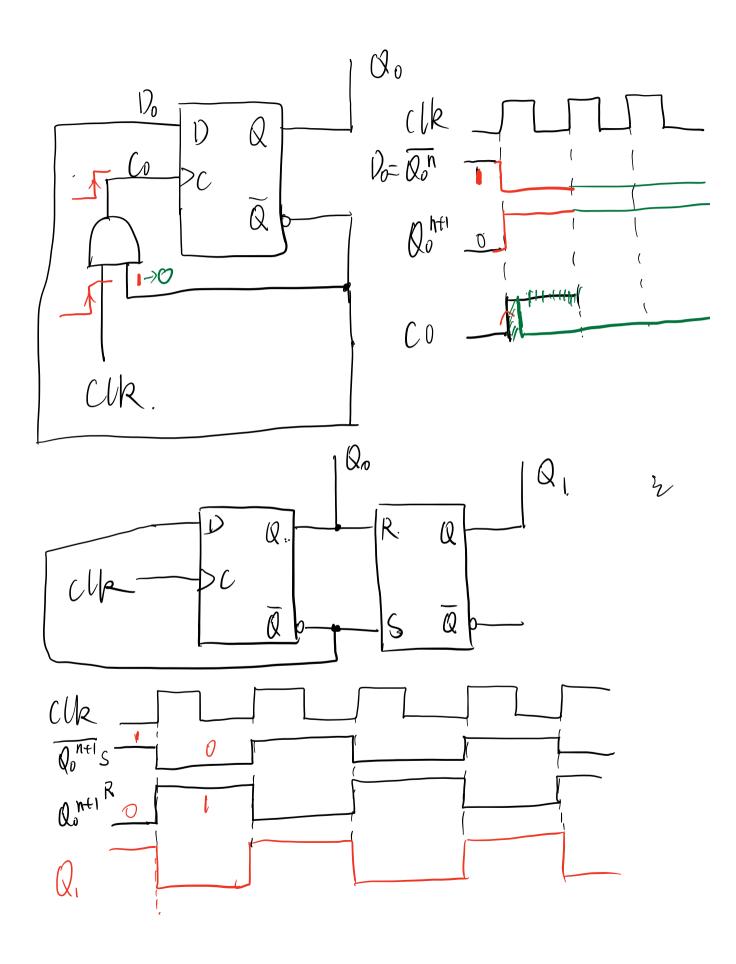

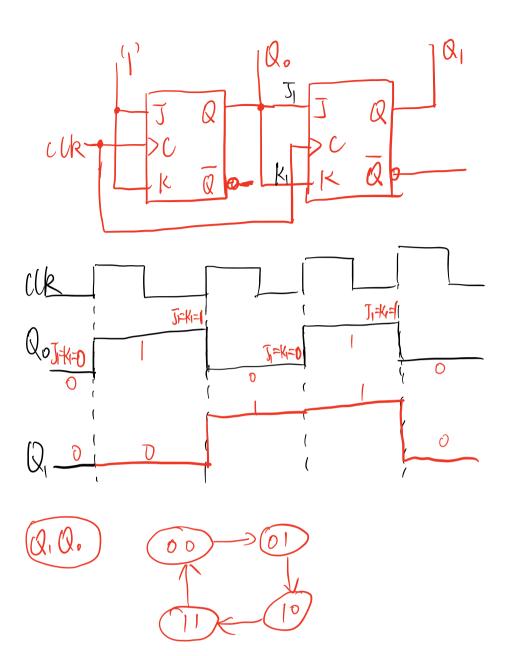

# **Counting**

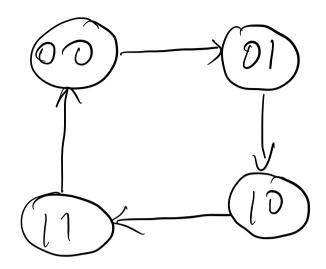

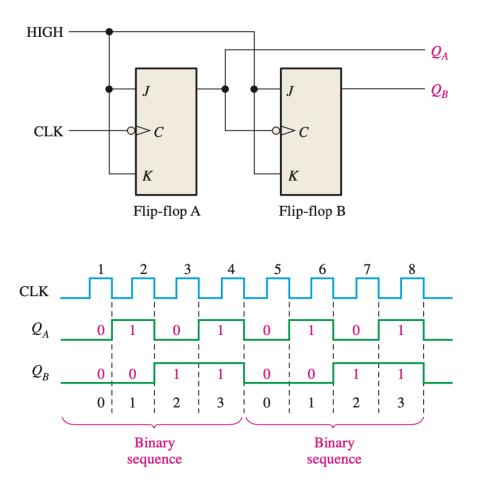

**FIGURE 7–40** J-K flip-flops used to generate a binary count sequence (00, 01, 10, 11). Two repetitions are shown.

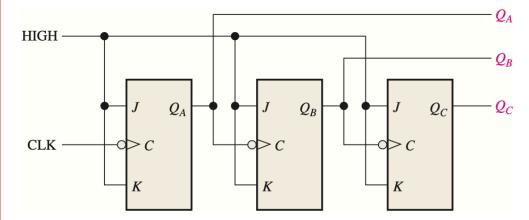

Determine the output waveforms in relation to the clock for  $Q_A$ ,  $Q_B$ , and  $Q_C$  in the circuit of Figure 7–41 and show the binary sequence represented by these waveforms.

FIGURE 7-41

# 7-5 One-Shots

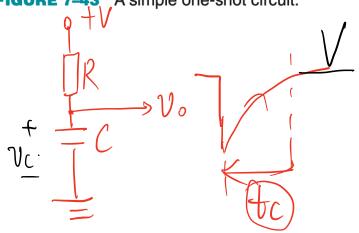

The **one-shot\***\*,\*\* also known as a **monostable** multivibrator, is a device with only one stable state. A one-shot is normally in its stable state and will change to its unstable state only when triggered. Once it is triggered, the one-shot remains in its unstable state for a prede-termined length of time and then automatically returns to its stable state. The time that the device stays in its unstable state determines the pulse width of its output.

$$V_{c}(0f) = V_{c}(0-) = 0V$$

$$V_{c}(\infty) = V$$

$$S = RC$$

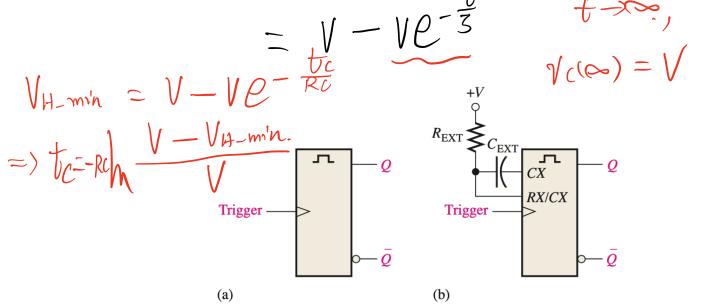

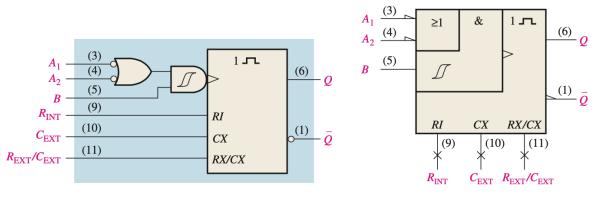

FIGURE 7-44 Basic one-shot logic symbols. CX and RX stand for external components.

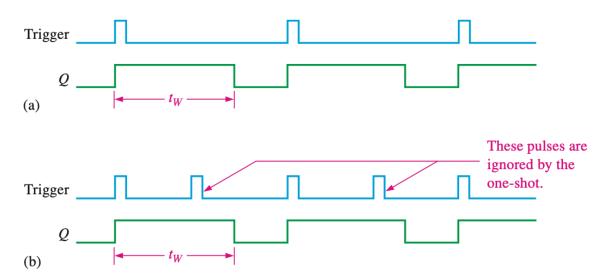

FIGURE 7-45 Nonretriggerable one-shot action.

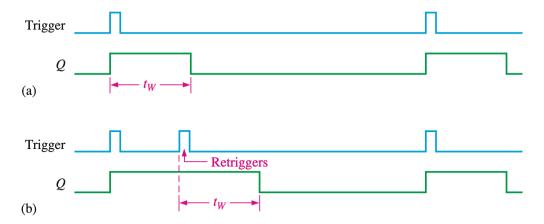

FIGURE 7-46 Retriggerable one-shot action.

# **Nonretriggerable One-Shot**

(a) Traditional logic symbol

(b) ANSI/IEEE std. 91–1984 logic symbol (X = nonlogic connection). "1 TL" is the qualifying symbol for a nonretriggerable one-shot.

FIGURE 7-47 Logic symbols for the 74121 nonretriggerable one-shot.

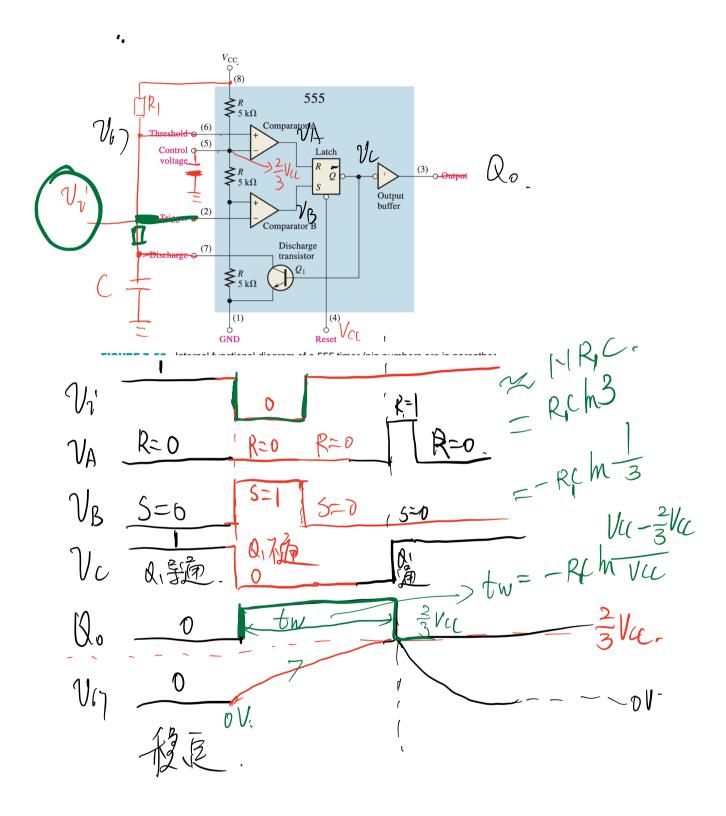

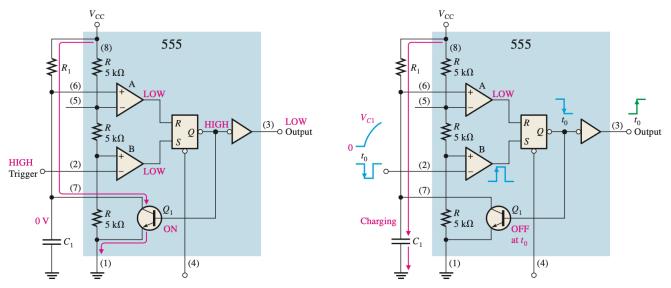

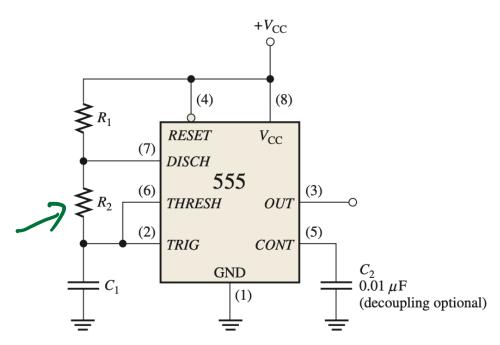

### The 555 Timer as a One-Shot

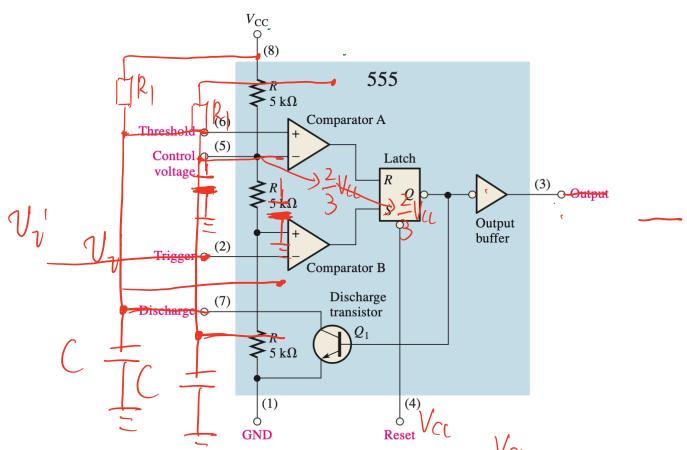

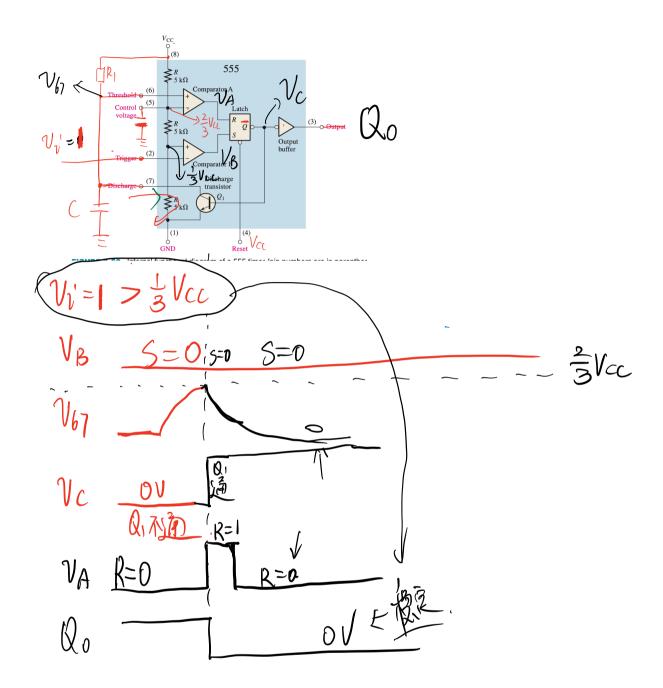

FIGURE 7–52 Internal functional diagram of a 555 timer (pin numbers are in parentheses).

Monostable (One-Shot) Operation

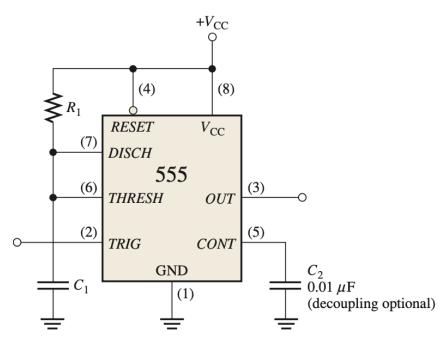

**FIGURE 7–53** The 555 timer connected as a one-shot.

$$t_W=1.1R_1C_1$$

(a) Prior to triggering. (The current path is indicated by the red arrow.)

(b) When triggered

(c) At end of charging interval

FIGURE 7-54 One-shot operation of the 555 timer.

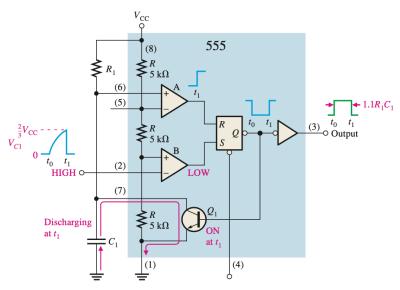

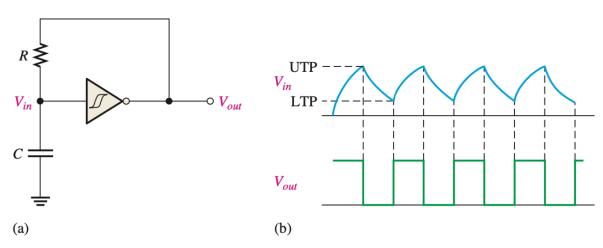

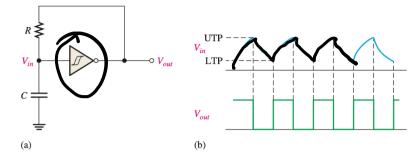

# 7-6 The Astable Multivibrator

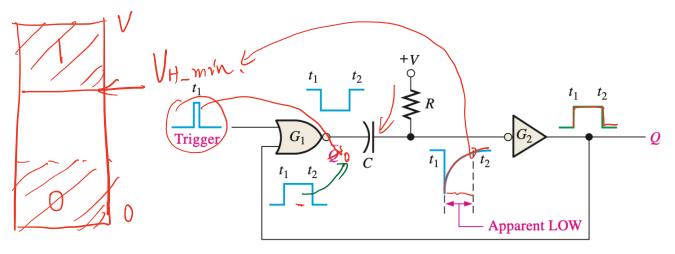

FIGURE 7-55 Basic astable multivibrator using a Schmitt trigger.

FIGURE 7-55 Basic astable multivibrator using a Schmitt trigger.

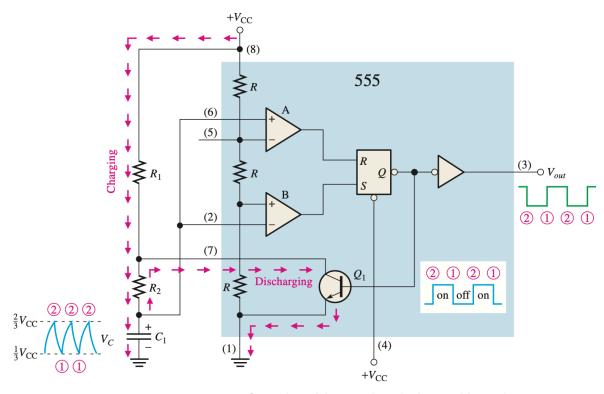

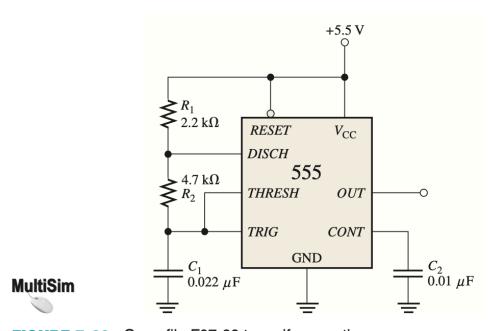

## The 555 Timer as an Astable Multivibrator

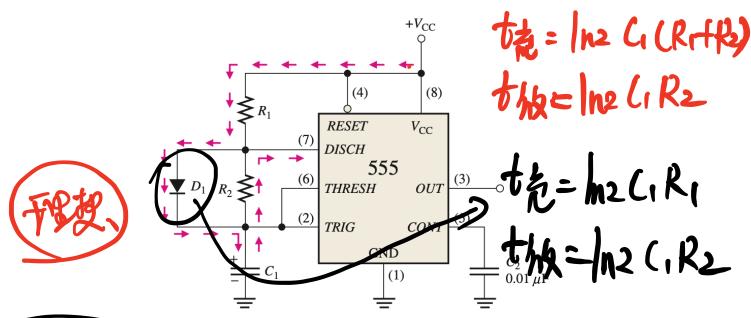

FIGURE 7-56 The 555 timer connected as an astable multivibrator (oscillator).

FIGURE 7-57 Operation of the 555 timer in the astable mode.

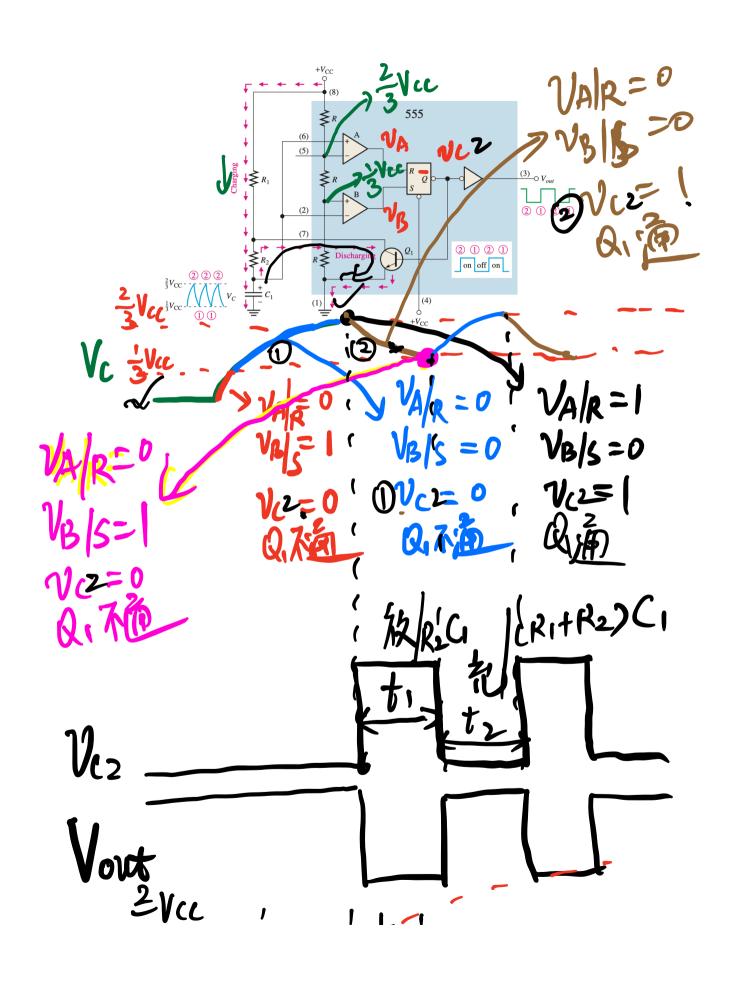

$$f=rac{1.44}{(R_1+2R_2)C_1} \ t_H=0.7(R_1+R_2)C_1 \ t_L=0.7R_2C_1$$

$$V_{c} = \frac{1}{3}V_{cc} = \frac{1}$$

$$t_{1}; V_{c}(04) = \frac{2}{3}V_{cc} V_{c}(\infty) = 0$$

$$V_{c}(t_{1}) = \frac{1}{3}V_{cc} 5 = R_{2}C_{1}$$

$$V_{c}(t_{1}) = 0 + \left(\frac{2}{3}V_{cc} - 0\right) e^{-\frac{1}{R_{2}C_{1}}}$$

$$V_{c}(t_{1}) = \frac{1}{3}V_{cc} + t_{1}$$

$$= \frac{1}{3}V_{cc} + t_{1}$$

$$= \frac{2}{3}V_{cc} + t_{2}$$

$$= \frac{2}{3}V_{cc} + t_{1}$$

$$= \frac{2}{3}V_{cc} + t_{2}$$

$$= \frac{2}{3}V_{cc} + t_{1}$$

$$= \frac{2}{3}V_{cc} + t_{2}$$

$t_1 = R_2 (1 \ln 2) t_2 = (R_1 + R_2) (1 \ln 2)$ =)  $T = t_1 + t_2$ =  $(R_1 + 2R_2) (1 \ln 2)$

$$Duty\ cycle = rac{t_H}{T}$$

**FIGURE 7–39** The addition of diode  $D_1$  allows the duty cycle of the output to be adjusted to less than 50 percent by making  $R_1 < R_2$ .

#### EXAMPLE /-14

A 555 timer configured to run in the astable mode (pulse oscillator) is shown in Figure 7–60. Determine the frequency of the output and the duty cycle.

**FIGURE 7–60** Open file F07-60 to verify operation.